0. 3D 반도체

0.1. 3D 반도체는 소자 설계 방식의 근본적인 변화 필요

0.2. 새로운 소재, 새로운 증착 및 식각 방식 필요

0.3. 2차원 반도체 제조 방법 및 한계

0.3.1. 평평한 실리콘 시트 사용, 표면에 다양한 구조 배치 후 와이어를 통한 연결

0.3.2. 층층이 증착된 재료에, 포토리소그래피 (Photolithography)를 이용한 패턴 형성, 노출 영역 식각, 최종 필요 피처(Feature) 구현.

0.3.3. 훨씬 더 좁은 공간에 더 많은 회로 배치 요구 증가, 점점 더 복잡해져가는 공정

0.3.4. 그결과 2D 구조물 제작 비용 증가 지속 및 2차원 평면 스케일링의 한계에 도달

0.4. 3D 구조의 반도체가 대안으로 등장.

0.4.1. 3D 웰(well) 지지 가능한 고선택비 식각 용도 개발시작. 패키징, 비휘발성 메모리 및 트랜지스터까지 적용 검토 시작.

1. 트랜지스터 3D

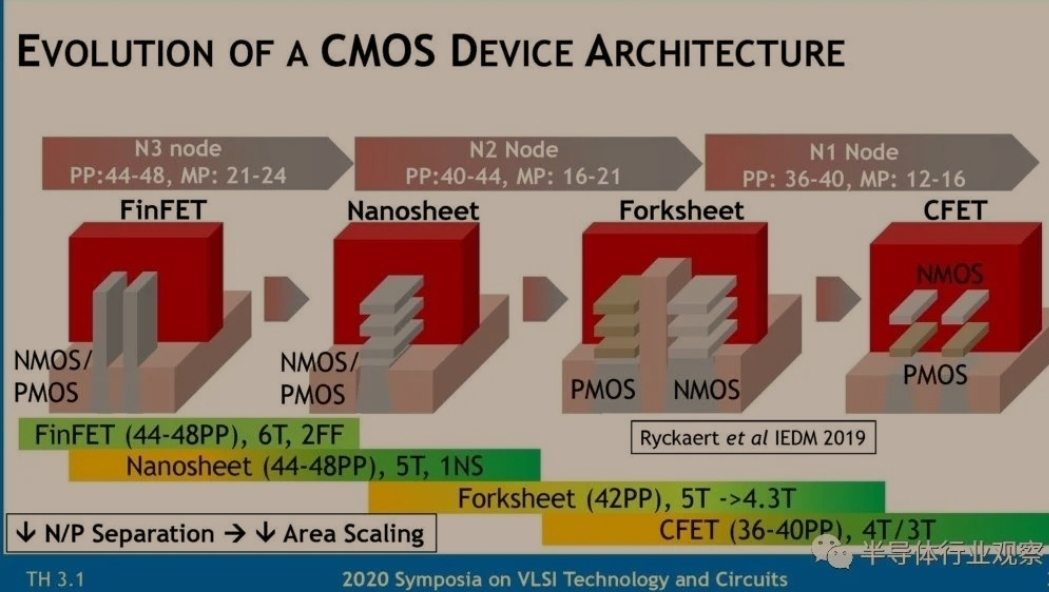

1.1. 최초의 트랜지스터는 평평한 평면 형태, 트랜지스터 채널의 폭과 길이로 특성 결정

1.2. 게이트는 채널 위에 배치, 트랜지스터 동작을 제어, 채널 반대쪽과 밑면은 제어되지 않기 때문에 상대적으로 많은 제어량 필요

1.3. 핀펫: 3면의 게이트로 제어가능한 채널용 핀 도입, 평면 트랜지스터의 첫 번째 변화

1.4. 게이트 올 어라운드(Gate-All-Around, GAA) 트랜지스터: 게이트가 채널을 완전히 감싸며, 여러 개의 와이어나 시트를 제조, 4개 면 제어 가능.

2. 플래시메모리 적층

2.1. NAND 플래시 메모리의 수평 스트링 메모리 비트(bit)를 위쪽으로 쌓는 방법으로 3차원 구조 적용

2.2. 수직 배열시 얇은 물질 레이어(layers of materials)를 번갈아 가며 최대한 많은 레이어 적층

2.3. 한 레이어의 비트가 다른 레이어의 모든 비트의 치수와 동일하게끔, 모든 레이어의 두께가 균일하고 100% 평평하도록 구현

2.4. 각 레이어 상호간 연결을 위해서 레이어 스택 형성, 스택을 관통하는 구멍을 식각으로 구현, 구멍에 적절한 연결 물질을 채워넣음.정밀하고 까다로운 식각 및 증착 작업 필요.

2.5. 이런 어려움으로 인해 스택 하나 들어가는 레이어 수 한계 존재, 레이어 수 확장 관련 새로운 방법 필요

3. 3D DRAM

3.1. 3D 패키징

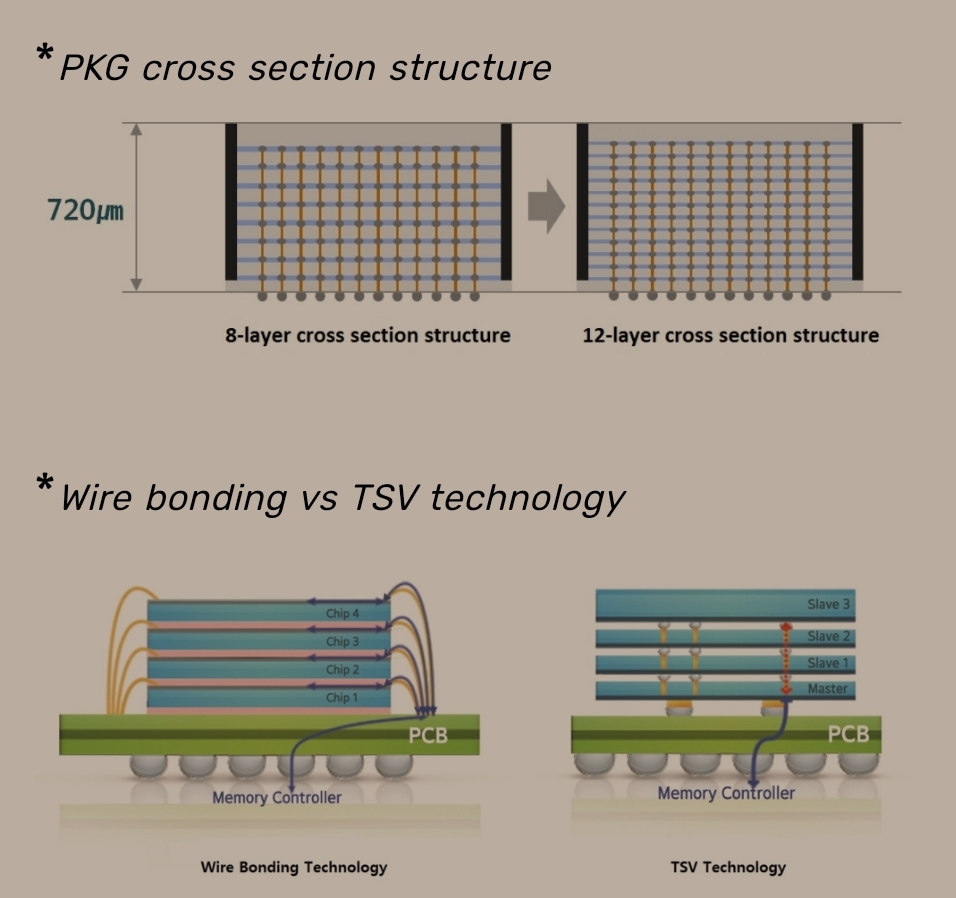

3.1.11. 인쇄회로 기판(PCB)에 설치하기 위해 칩은 패키징 처리 되어야 함.

3.1.2. 즉, 지금까지의 패키지는 단순히 섬세한 실리콘 칩을 보호 및 보드에 연결해주는 용도에 국한.

3.1.3. 현재는 1개의 패키지에 칩 여러 개 동시에 설치 경우 증가, 이 공간을 줄이려는 목적으로 3D 구조 도입. '3D 패키징'

3.1.4. 3D 패키징 내부의 여러개의 칩 적층시, 칩과 칩 사이 연결부의 밀도를 증가시켜야 하고, 이 연결부는 여러 신호를 동시에 전송, 결과적으로 신호 속도 향상

3.1.5. 스택의 칩이 두 개 이상일 경우, 스택보다 위에 있는 칩과의 연결을 위해서 “실리콘 관통 전극(Through-Silicon Via, TSV)” 적용.

3.1.6. 3D 칩 스태킹(stacking)는 메모리에 우선 적용, 그중에서 고대역폭 메모리(High-Bandwidth Memory, HBM)우선 적용 중.

리소그래피는 한 번에 여러 층에 영향을 줘야 하는데 아직 사용할 수 있는 대량생산 공정이 없는 상태다.